Hola a todos. En este segundo artículo dedicado a los transistores unipolares JFET (también denominados FET a secas), vamos a ver un poco mas de sus características y una determinada forma de polarizarlos, que os adelanto que no es la mas adecuada.

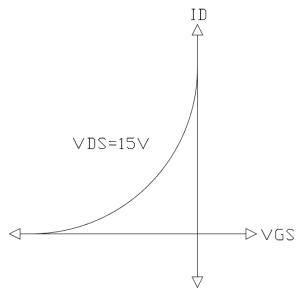

Veamos la curva siguiente, a la que llamaremos curva de transconductancia:

Podemos apreciar a simple vista que este curva no es lineal. En esta curva mantenemos la tensión drenador-surtidor fija (15 voltios) y variando la tensión de puerta observamos como varía la corriente de drenador.

De la anterior curva, se extrae la formula siguiente:

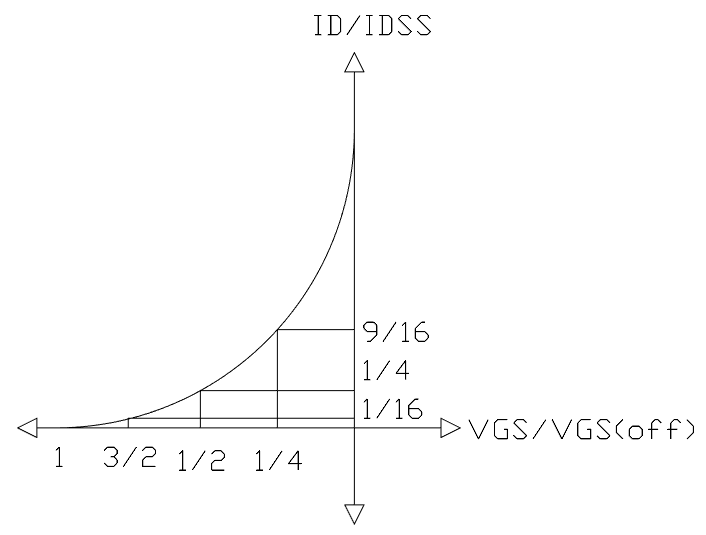

Por otra parte, de la anterior curva se puede obtener una curva normalizada. Esta quedaría de la siguiente forma:

Esta estructura de curva se cumple siempre.

Para poner un ejemplo: Si la tensión puerta-surtidor es la mitad (1/2) tendremos que la corriente de surtidor es 1/4 de la máxima. Con el resto de valores también se cumple.

Vamos a ver a continuación una forma de polarizar el transistor, que es hacerlo en la región óhmica, que es donde el FET se comporta como una resistencia.

Esta polarización no es demasiado eficiente, ya que por ejemplo para el 2N5459, la tensión VGS(off) puede variar entre -2 y -8 voltios, lo cual hace que la corriente IDSS pueda fluctuar entre 4 y 16 miliamperios. Esto repercute en el punto Q, que no es precisamente estable.

Todo esto que acabo de comentar, se puede apreciar en la siguiente gráfica:

Todos estos datos figuran en el datasheet y figuran marcados en rojo en el articulo anterior (transistor 2N5459).

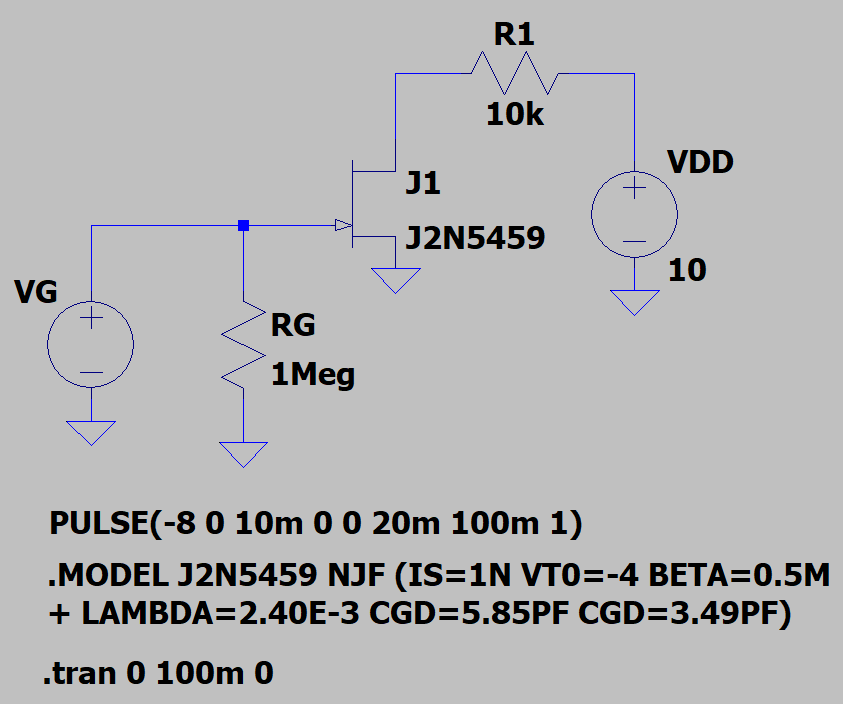

Para polarizar un transistor FET en la región óhmica, se podría utilizar la polarización de puerta. Ver figura siguiente:

Veamos un ejemplo de polarización de puerta.

En la puerta le colocamos una fuente que va a generar una serie de pulsos.

Primeramente le vamos a meter -8 voltios para estrangularlo durante 10 milisegundos. Seguidamente le introducimos 0 voltios para que conduzca al máximo la IDSS y el resto de tiempo esterará estrangulado (sin conducción).

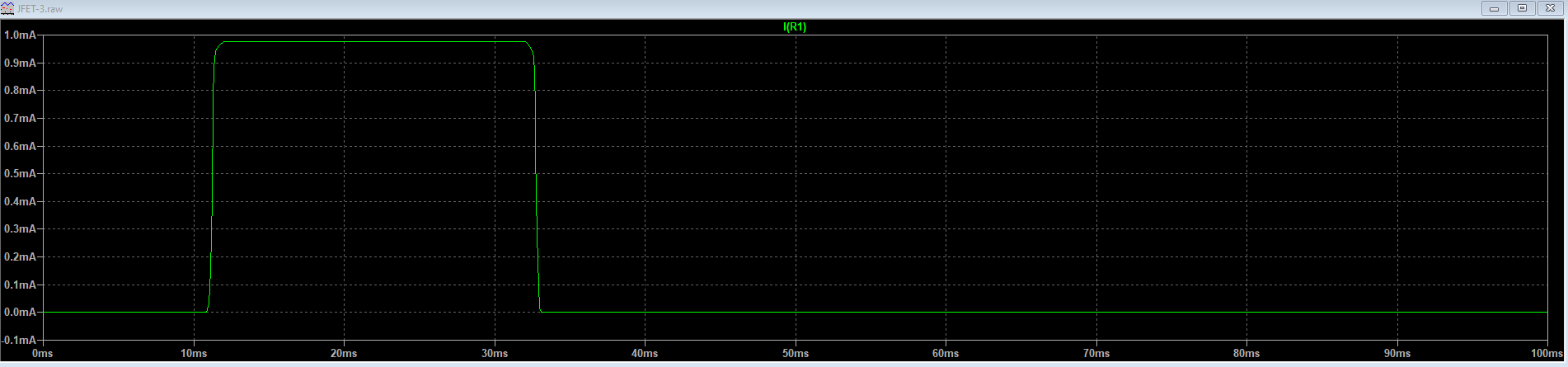

La señal de salida será esta:

Y con esto concluimos el artículo de hoy dedicado a los JFETs. En el artículo siguiente seguiré monos adentrándonos en el mundo de los transistores de este tipo.

Podéis descargar el esquema desde este enlace.

Un cordial saludo. 🙂

REFERENCIAS:

Principios de Electrónica, séptima edición. Albert Malvino, David J. Bates